# Sil8784 Multi-format Analog Video Front-end with HDMI/MHL Transmitter

**Data Sheet**

Sil-DS-1122-C

June 2017

# Contents

| 1. | Gene           | eral Description                     | 5 |

|----|----------------|--------------------------------------|---|

|    | 1.1.           | Features                             | 5 |

|    | 1.1.1          | 1. Analog Video Front-end            | 5 |

|    | 1.1.2          | 2. Multi-format Video Decoder        | 5 |

|    | 1.1.3          | 3. Video Processing                  | 5 |

|    | 1.1.4          | 4. HDMI/MHL Transmitter              | 5 |

|    | 1.2.           | Applications                         | 5 |

|    | 1.3.           | Packaging                            | 5 |

|    | 1.4.           | Temperature Range                    | 5 |

| 2. | Prod           | luct Family                          | 6 |

| 3. |                | ctional Description                  |   |

|    | 3.1.           | Analog Front-end                     |   |

|    | 3.1.1          |                                      |   |

|    | 3.1.2          |                                      |   |

|    | 3.1.3          |                                      |   |

|    | 3.1.4          |                                      |   |

|    | 3.1.5          |                                      |   |

|    | 3.1.6          | 1                                    |   |

|    | 3.1.7          |                                      |   |

|    |                | Video Decoder (VDC)                  |   |

|    | 3.2.1          |                                      |   |

|    | 3.2.2          | -1                                   |   |

|    | 3.2.3          |                                      |   |

|    |                | Video Processing                     |   |

|    | 3.3.1          |                                      |   |

|    | 3.3.2          |                                      |   |

|    | 3.3.3          |                                      |   |

|    | 3.3.4          |                                      |   |

|    | 3.3.5          |                                      |   |

|    | 3.3.6          |                                      |   |

|    | 3.3.7          |                                      |   |

|    |                | Dual-mode HDMI/MHL Transmitter       |   |

|    | 3.4.1          |                                      |   |

|    | 3.4.2          | ···· 8 ···                           |   |

|    | 3.4.3          |                                      |   |

|    |                | Control Logic                        |   |

|    | 3.5.1          |                                      |   |

|    | 3.5.2          |                                      |   |

|    | 3.5.3          |                                      |   |

|    | 3.5.4<br>3.5.5 |                                      |   |

| 4. |                | trical Specifications                |   |

| 4. | 4.1.           | Absolute Maximum Conditions          |   |

|    |                | Normal Operating Conditions          |   |

|    | 4.2.           | · •                                  |   |

|    | -              | ESD Specifications                   |   |

|    |                | AC Specifications                    |   |

|    | 4.5.           | Control Signal Timing Specifications |   |

| 5. |                | ng Diagrams                          |   |

| ٦. |                | I <sup>2</sup> C Bus Timing Diagrams |   |

|    |                | Reset Timing Diagram                 |   |

|    | 5.3.           | Audio Timing Diagrams                |   |

|    |                | 0                                    |   |

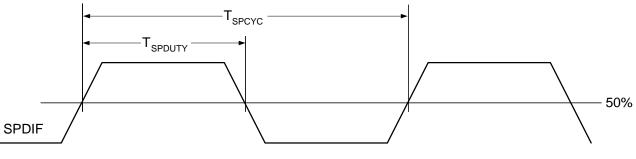

| 6.  | Pin l        | Diagra  | am and Description             | 33 |

|-----|--------------|---------|--------------------------------|----|

| 6   | 5.1.         | Pin D   | Diagram                        | 33 |

| 6   | 5.2.         | Pin D   | Descriptions                   | 34 |

|     | 6.2.         | 1.      | AFE Pins                       | 34 |

|     | 6.2.2        | 2.      | Audio Input Pins               | 35 |

|     | 6.2.         | 3.      | Configuration and Control Pins | 36 |

|     | 6.2.4        | 4.      | HDMI/MHL Data Pins             | 37 |

|     | 6.2.         | 5.      | SPI Interface Pins             | 37 |

|     | 6.2.         | 6.      | Power and Ground Connections   | 38 |

|     | 6.2.         | 7.      | Crystal Pins                   | 38 |

|     | 6.2.         | .8.     | Reserved Pins                  | 38 |

| 7.  | Desi         | ign Re  | commendations                  | 39 |

| 7   | 7.1.         | Туріс   | cal Connections                | 39 |

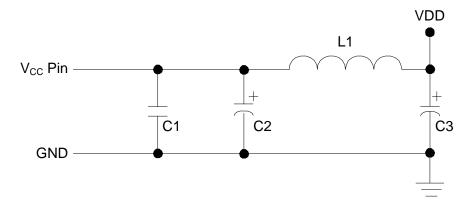

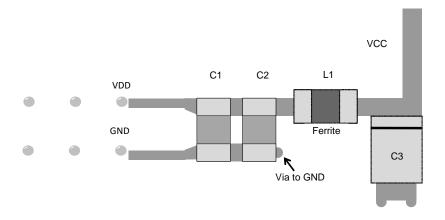

| 7   | <i>'</i> .2. | Powe    | er Supplies Decoupling         | 41 |

| 7   | <b>'</b> .3. | High    | -speed HDMI/MHL TMDS Signals   | 42 |

|     | 7.3.         | 1.      | Source Termination             | 42 |

|     | 7.3.         | 2.      | ESD Protection                 | 42 |

|     | 7.3.         | 3.      | Layout Guidelines              | 42 |

| 7   | <b>'</b> .4. | EMI     | Considerations                 | 42 |

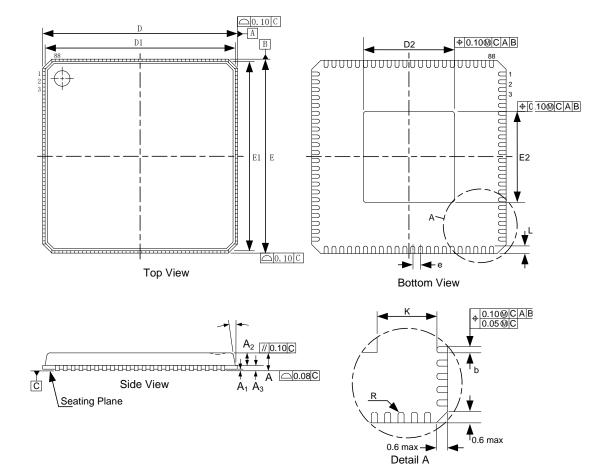

| 8.  | Pack         | kaging  | ,                              | 43 |

| ξ   | 3.1.         | ePad    | Requirements                   | 43 |

| 8   | 3.2.         | Pack    | age Dimensions                 | 44 |

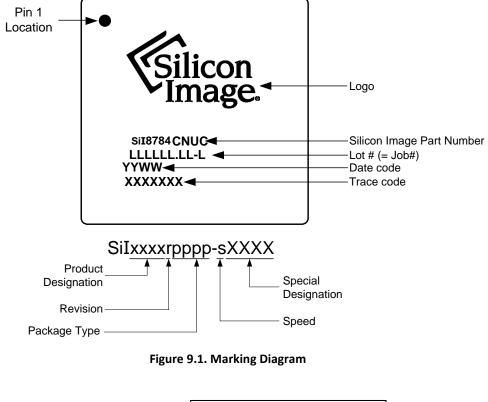

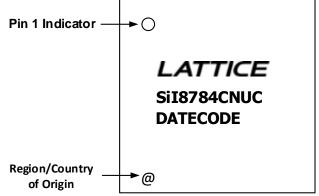

| 9.  | Mar          | rking S | Specification                  | 45 |

| 9   | 9.1.         | Orde    | ring Information               | 45 |

| Ref | erenc        | ces     |                                | 46 |

| 5   | tanda        | ards D  | ocuments                       | 46 |

| L   | attice       | e Semi  | conductor Documents            | 46 |

| Re۱ | vision       | Histor  | γ                              | 47 |

# **Figures**

| Figure 1.1. Typical Application of the Sil8784 Device                                         | 5  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 1.1. Typical Application of the Sil8784 Device<br>Figure 3.1. Functional Block Diagram | 7  |

| Figure 3.2. Clamp and Offset                                                                  |    |

| Figure 3.3. Sync Slicers                                                                      | 10 |

| Figure 3.4. CVBS Processing Diagram                                                           | 11 |

| Figure 3.5. Component/RGB Processing Diagram                                                  | 12 |

| Figure 3.6. Dual-mode HDMI/MHL Transmitter Diagram                                            | 15 |

| Figure 3.7. Transmitter Video Data Processing Path Embedded Sync Decoder                      | 16 |

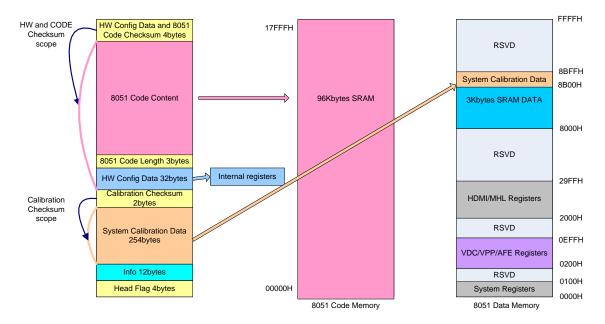

| Figure 3.8. External Memory Structure                                                         | 19 |

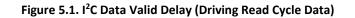

| Figure 5.1. I <sup>2</sup> C Data Valid Delay (Driving Read Cycle Data)                       |    |

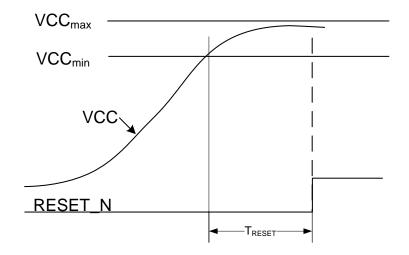

| Figure 5.2. Conditions for Use of RESET_N                                                     | 31 |

| Figure 5.3. RESET_N Minimum Timings                                                           | 31 |

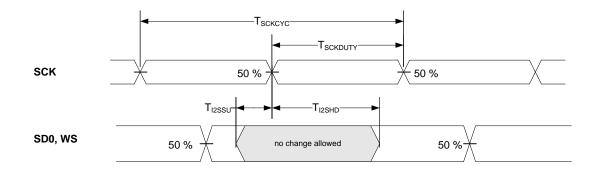

| Figure 5.4. I <sup>2</sup> S Timings                                                          | 32 |

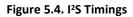

| Figure 5.5. S/PDIF Timings                                                                    | 32 |

| Figure 6.1. Pin Diagram                                                                       | 33 |

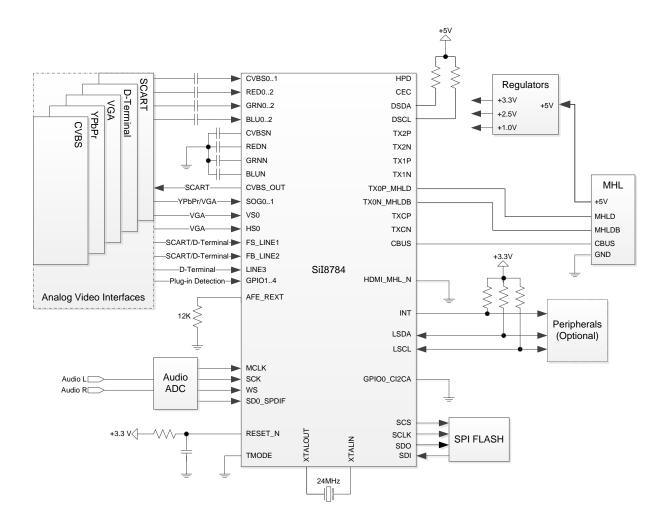

| Figure 7.1.Typical Connection Diagram (MHL Output)                                            | 39 |

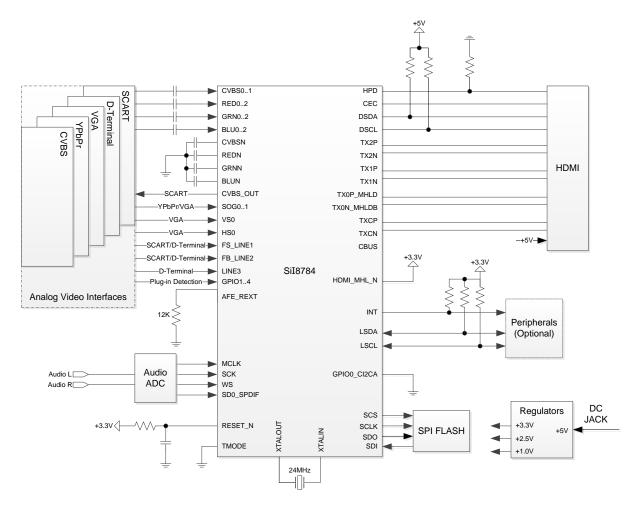

| Figure 7.2.Typical Connection Diagram (HDMI Output)                                           | 40 |

| Figure 7.3. Decoupling and Bypass Schematic                                                   | 41 |

| Figure 7.4. Decoupling and Bypass Capacitor Placement                                         | 41 |

| Figure 8.1. 88-Pin QFN Package Diagram                                                        | 44 |

| Figure 9.1. Marking Diagram                                                                   |    |

| Figure 9.2. Alternate Topside Marking                                                         |    |

# Tables

| Table 2.1. Product Selection Guide                                            |    |

|-------------------------------------------------------------------------------|----|

| Table 3.1. Inputs Configuration with SCART Interface                          |    |

| Table 3.2. Inputs Configuration with D-Terminal Interface                     |    |

| Table 3.3. Supported Standards                                                |    |

| Table 3.4. Color Space Versus Video Format                                    |    |

| Table 3.5. YCbCr-to-RGB Color Space Conversion Formula                        | 17 |

| Table 3.6. Supported MCLK Frequencies                                         | 18 |

| Table 3.7. Head Flags                                                         | 19 |

| Table 3.8. Info Bytes                                                         | 20 |

| Table 3.9. SPI Parameter                                                      | 20 |

| Table 3.10. Calibration Checksum                                              |    |

| Table 3.11. HW Configuration Data                                             | 20 |

| Table 3.12. 8051 Code Size                                                    | 20 |

| Table 3.13. HW Configuration Data and Code Checksum                           | 20 |

| Table 3.14. Control of Transmitter I <sup>2</sup> C Address with CI2CA Signal | 21 |

| Table 3.15. List of GPIOs                                                     | 22 |

| Table 4.1. Absolute Maximum Ratings                                           | 23 |

| Table 4.2. Normal Operating Conditions                                        | 24 |

| Table 4.3. ESD Specifications                                                 | 25 |

| Table 4.4. Digital I/O Specifications                                         | 26 |

| Table 4.5. HDMI TMDS Output DC Specifications                                 |    |

| Table 4.6. MHL TMDS Output DC Specifications                                  |    |

| Table 4.7. CBUS DC Specifications                                             | 27 |

| Table 4.8. Analog Front-end Electrical Specifications                         | 28 |

| Table 4.9. HDMI/MHL Output AC Timing Specifications                           |    |

| Table 4.10. CBUS Timing Specifications                                        | 29 |

| Table 4.11. I <sup>2</sup> S Audio Input Port Timing Specifications           | 30 |

| Table 4.12. S/PDIF Input Port Timing Specifications                           | 30 |

| Table 4.13. Control Signal Timing Specifications                              | 30 |

| Table 6.1. AFE Input/Output Pins                                              | 34 |

| Table 6.2. Audio Input Pins                                                   | 35 |

| Table 6.3. Configuration and Control Pins                                     | 36 |

| Table 6.4. HDMI/MHL Data Pins                                                 | 37 |

| Table 6.5. SPI Interface Pins                                                 | 37 |

| Table 6.6. Power and Ground Connections                                       | 38 |

| Table 6.7. Reserved Pins                                                      | 38 |

|                                                                               |    |

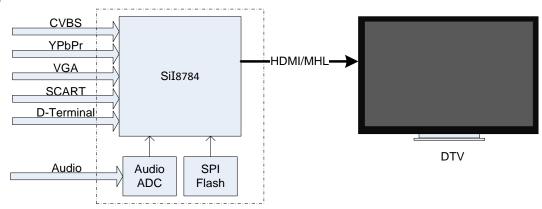

# 1. General Description

The Lattice Semiconductor Sil8784 device is a high quality, multi-format analog video decoder and processor with an integrated dual-mode High Definition Multimedia Interface (HDMI<sup>®</sup>)/Mobil High-definition Link (MHL<sup>®</sup>) transmitter. A microcontroller is integrated to reduce the system Bill Of Materials (BOM) cost.

The Sil8784 device supports worldwide PAL, NTSC and SECAM standards, YPbPr video signals up to 1080p @ 60 Hz resolution, and RGB graphics signals from VGA to UXGA resolutions. It also supports the SCART interface with Fast Blanking and the D-Terminal.

This device contains a Time Base Correction (TBC) module, a de-interlacer with a post-processor engine, and a VBI decoder. For content protected analog videos, HDCP will automatically be enabled on the HDMI or MHL output.

# 1.1. Features

# 1.1.1. Analog Video Front-end

- Four 10-bit Analog to Digital Convertors (ADC) sampling up to 170 MHz

- Flexible input multiplexers to support composite, component, VGA, SCART with Fast Blanking and D-Terminal interfaces

- Supports cable plug-in detection and active video signal detection

# 1.1.2. Multi-format Video Decoder

- Automatic format detection

- Supports NTSC, PAL, and SECAM standards of composite input with adaptive comb filter

- Supports 240p, 480i/p, 576i/p, 720p, 1080i/p component video

- Supports RGB graphics from VGA to UXGA

- Supports Macrovision Type I, II, III copy protection detection

- Supports multi-standard VBI decoding: Teletext, WSS, VPS, CC, CGMS, and V-CHIP

# 1.1.3. Video Processing

- Time Base Correction

- De-interlacer with Edge Smoothing

- Automatic Phase/Position Detection

# 1.1.4. HDMI/MHL Transmitter

- Selectable HDMI/MHL Dual-mode

- Compliant with HDMI 1.4b and MHL 2.1 specifications

- HDMI output up to 1080p @ 60 Hz or UXGA @ 60 Hz resolution

- MHL output up to 1080p @ 60 Hz resolution

- HDCP 1.4

- Audio insertion with I<sup>2</sup>S/ SPDIF input

- VBI data forwarding over HDMI/MHL

# 1.2. Applications

The Sil8784 device is targeted for the Digital TV (DTV) market.

# 1.3. Packaging

- 88-pin QFN with exposed pad (ePad)

- 10 mm × 10 mm × 0.9 mm

# 1.4. Temperature Range

• 0 °C to +70 °C

## Figure 1.1. Typical Application of the Sil8784 Device

# 2. Product Family

A comparison of the features between the SiI8784 device and the SiI8788 device is shown in Table 2.1.

#### Table 2.1. Product Selection Guide

| Feature                                     | Sil8784              | Sil8788 |  |  |  |  |  |  |

|---------------------------------------------|----------------------|---------|--|--|--|--|--|--|

| Analog Video Input                          |                      | ·       |  |  |  |  |  |  |

| Component (YP <sub>b</sub> P <sub>r</sub> ) | YES                  | YES     |  |  |  |  |  |  |

| Composite (CVBS)                            | YES                  | YES     |  |  |  |  |  |  |

| D-Terminal                                  | YES                  | NO      |  |  |  |  |  |  |

| RGB graphics (VGA)                          | YES                  | NO      |  |  |  |  |  |  |

| SCART with Fast Blanking                    | YES                  | NO      |  |  |  |  |  |  |

| Digital Video Output                        | Digital Video Output |         |  |  |  |  |  |  |

| Parallel                                    | NO                   | YES     |  |  |  |  |  |  |

| HDMI                                        | YES                  | NO      |  |  |  |  |  |  |

| MHL                                         | YES                  | NO      |  |  |  |  |  |  |

| Audio Input                                 |                      |         |  |  |  |  |  |  |

| SPDIF Input                                 | YES                  | NO      |  |  |  |  |  |  |

| I <sup>2</sup> S Input                      | YES                  | NO      |  |  |  |  |  |  |

| Package                                     |                      |         |  |  |  |  |  |  |

| Package Type                                | QFN                  | QFN     |  |  |  |  |  |  |

| Pin Count                                   | 88                   | 88      |  |  |  |  |  |  |

# 3. Functional Description

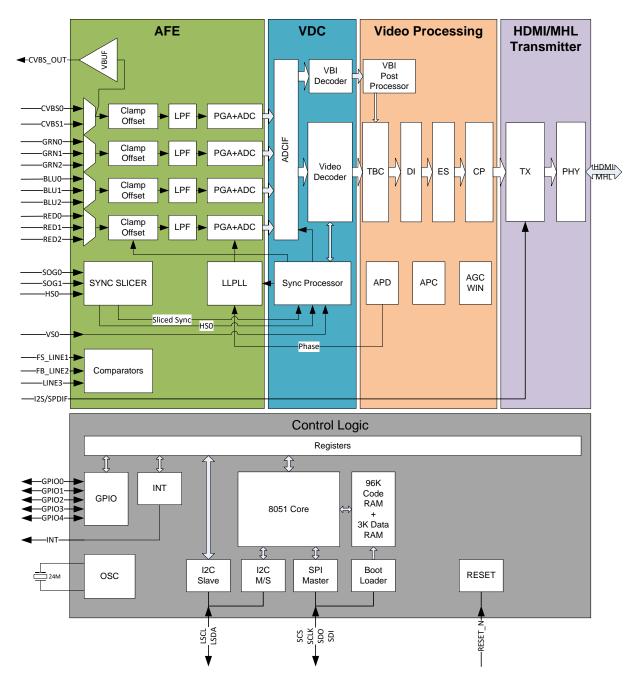

The Sil8784 device has four subblocks in its signal path and one control block: Analog Front-end (AFE), Video Decoder (VDC), Video Processing, HDMI/MHL transmitter and Control Logic. Figure 3.1 shows the block diagram.

Figure 3.1. Functional Block Diagram

Each subblock is described in the following sections.

# 3.1. Analog Front-end

The Analog Front-end (AFE) provides four input channels for CVBS, R, G, and B. Each channel includes an Input Multiplexer, a Clamp and Offset DAC, a Programmable Low-pass Filter, and a high quality 10-bit ADC with Programmable Gain Amplifier. In addition, there is a Line Locked PLL to generate sampling clocks for ADCs, Sync Slicers to handle SOG signals, a set of input comparators to support SCART and D-terminal interfaces, and a CVBS output buffer to support SCART.

# 3.1.1. Input Multiplexer

The Sil8784 device provides two CVBS inputs, and three R/G/B inputs for flexible configurations. Table 3.1 and Table 3.2 show some examples.

| rabie orzi nipa |       |       |      |      |      |      |      |      |      |      |      |

|-----------------|-------|-------|------|------|------|------|------|------|------|------|------|

| -               | CVBS0 | CVBS1 | RED0 | RED1 | RED2 | GRN0 | GRN1 | GRN2 | BLU0 | BLU1 | BLU2 |

| CVBS            | CVBS  | —     | -    | -    | -    | —    | —    | —    | —    | -    | -    |

| Component       | —     | —     | -    | Pr   | _    | —    | Y    | —    | —    | Pb   | -    |

| VGA             | —     | —     | _    | _    | R    | —    | —    | G    | —    |      | В    |

| SCART           | _     | CVBS  | R    | _    | _    | G    | _    | —    | В    | _    | _    |

## Table 3.1. Inputs Configuration with SCART Interface

## Table 3.2. Inputs Configuration with D-Terminal Interface

| _          | CVBS0 | CVBS1 | RED0 | RED1 | RED2 | GRN0 | GRN1 | GRN2 | BLU0 | BLU1 | BLU2 |

|------------|-------|-------|------|------|------|------|------|------|------|------|------|

| CVBS       | CVBS  | —     | -    | _    | -    | —    | —    | —    | -    | —    | _    |

| Component  | _     | _     | _    | Pr   | _    | _    | Y    | _    | -    | Pb   | _    |

| VGA        | _     | _     | _    | -    | R    | _    | _    | G    | -    | _    | В    |

| D-Terminal | _     | _     | Pr   | _    | _    | Y    | _    | —    | Pb   | _    | _    |

# 3.1.2. Clamp and Offset

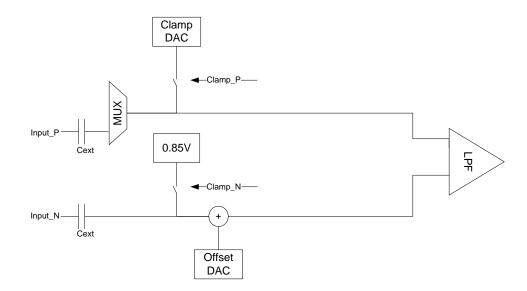

As most of the video signals, such as CVBS, are AC coupled, their DC component is lost during the transmission. A voltage type clamp circuit is positioned in front of each channel to restore the DC component.

Figure 3.2. Clamp and Offset

The clamp DAC output voltage is 3-bit programmable and AFE provides more accurate 10-bit  $\pm 0.5$  V output offset DAC to keep the input signal within the ADC input range. The offset level can be controlled automatically by ADCIF block of VDC or manually by software.

# 3.1.3. Low-pass Filter

The Low-pass Filter (LPF) is a first order analog filter to remove the out-of-band noise from video signal. Its –3 dB bandwidth can be set to 600 MHz (Bypass), 400 MHz, 200 MHz, 100 MHz, or 50 MHz by software. Combined together with ADC over-sampling technology and the high order digital AA (Anti-alias) filter inside VDC, the Sil8784 device can meet the demand of overall AA performance.

# 3.1.4. ADC with Programmable Gain Amplifier

The ADC samples the input video signal and converts each sample into 10 bits digital data. It supports the sampling rates from 25 MSPS to 170 MSPS, and the sampling clock of CVBS channel can be independent with R, G, and B channels.

For the formats with lower pixel rate, oversampling is recommended. The Sil8784 device supports 2X, 4X and 8X oversampling.

The Programmable Gain Amplifier (PGA) in the front stage of ADC has a nominal gain range from –6 dB to +6 dB, so the Sil8784 device can adapt to a wide range of input video signal levels, especially the CVBS signal from an RF tuner. The PGA can be controlled either automatically by the gain control function of VDC or manually by software.

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# 3.1.5. Line Locked PLL (LLPLL)

The Line Locked PLL (LLPLL) is designed to generate the ADC sampling clock, i.e. pixel clock or oversampled pixel clock. It can be synchronized with a slower reference HSync pulses or run at a fixed frequency. The allowable input HSync range is from 15 kHz to 150 kHz, and the output pixel clock range is from 25 MHz to 170 MHz.

The LLPLL contains a high performance programmable digital PLL (DPLL) and an analog PLL (APLL) which generates the high frequency reference clock needed by the DPLL from the 24 MHz crystal frequency.

The relative phase between the input sync pulse and the output clock of LLPLL can be adjusted in 32 steps by setting registers or automatically by the Auto Phase Detection (APD) block of the video processing module.

# 3.1.6. Sync Slicer

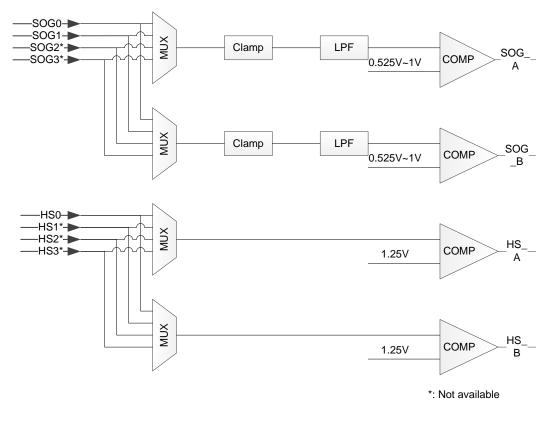

The Sync Slicer converts SOG and HSYNC signals into core domain digital signals. As shown in Figure 3.3, there are two sets of SOG slicers, each of contains an input multiplexer, a bottom level (0.5 V) clamp, a low pass filter, and a comparator. The comparator threshold is programmable. Also, there are two sets of HS slicers for TTL level syncs. When one of the slicers is configured as an active input, the other can be used to detect the activity of other inputs. This feature is helpful to implement the active channel detection and auto-switch functions.

Figure 3.3. Sync Slicers

# 3.1.7. Video Buffer (VBUF)

The Video Buffer (VBUF) buffers and outputs the selected CVBS input signal. This feature is useful to implement the CVBS return channel of the SCART interface. VBUF includes two major subblocks: clamp and voltage-to-current conversion. The Voltage-to-current conversion subblock converts the input signal to the output current which is proportional to the signal voltage level. A 75  $\Omega$  source termination resistor should be connected to the CVBS\_OUT output pin and signal ground.

# 3.2. Video Decoder (VDC)

The Sil8784 device provides a multi-format video decoder. VDC includes ADCIF, Sync Processor, adaptive 2D Comb decoder, and VBI Decoder blocks as shown in Figure 3.1 on page 7.

# 3.2.1. ADCIF

The ADCIF logic block contains Automatic Gain Control and Offset Calibration, and Anti-alias filtering and decimation subblocks. It also generates clamp pulses for clamp circuits at the proper time so that ADC is able to digitize the input analog within the proper range. The main indicator used to determine where the clamping position should be is the horizontal synchronization pulse coming from the Sync Processor block. Since this filtered HSync pulse may not always be correct, several layers of logic have been developed to ensure the clamping is not done at an incorrect position.

## 3.2.1.1. Automatic Gain Control and Offset Calibration

Parameters such as Sync Amplitude, Back Porch Levels are measured based on the HSync position, register controls, and logic executed in the Offset Gain Calculations sub block. These measured values are then used in determining the offset and gain adjustments. To ensure the stability and accuracy of digitized video signal, several control loops are built in the ADCIF block. These loops include Clamp, Coast, Gain, and Offset. The Clamp and Coast pulses, Gain and Offset parameters are generated by the ADCIF logic and directly connected to the AFE.

## 3.2.1.2. Anti-alias Filtering and Decimation

The Anti-aliasing (AA) filters remove high frequency noise from the raw digitized signals produced by the front-end video ADCs, and decimate the over-sampled video signal.

The AA filter has flexibility in the frequency response, sharp transition bandwidth, and good stop band attenuation. The AA filter allows the software to change the bandwidth of the filters as the signal conditions changes.

### 3.2.1.3. Video Decoder

Video Decoder block processes both CVBS data stream and component/RGB data stream. It also supports the SCART Fast Blanking functions.

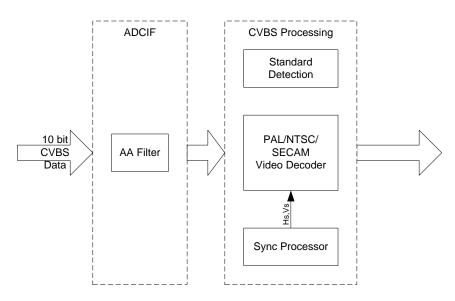

#### 3.2.1.4. CVBS Processing

CVBS Processing involves the Standard Detection, 2D Video Decoder, and Sync Processor subblocks, as shown in Figure 3.4 below.

#### Figure 3.4. CVBS Processing Diagram

The SiI8784 device can automatically detect NTSC (M/J/4.43), PAL (B/D/I/G/H/60/M/N/Nc), and SECAM (B/D/G/L/K) standards, and decode them properly.

An adaptive 2D comb filter is used in video decoder. The 2D comb filter has three output options, only horizontal filter, only vertical filter and blending of horizontal and vertical filter. When the current sample is on a horizontal transition edge, the vertical filter is selected. When the current sample is on a vertical transition edge, the horizontal filter is selected. When the above two phenomenon, the blending output is selected.

When the input signal is lost, the Sil8784 device can operate in a free-running mode to ensure a stable output.

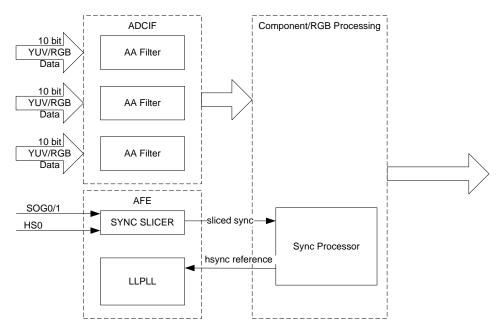

### 3.2.1.5. Component/RGB Processing

Component/RGB Processing processes Component Video and RGB Graphics. Component Video Processing includes Sync Processor. Figure 3.5 shows the block diagram of the component video and RGB Graphics processing. The following sections explain each of the blocks in detail.

Figure 3.5. Component/RGB Processing Diagram

The Sil8784 device supports 480i/576i, 480p/576p, 720p, 1080i, and 1080p for standard and high definition resolutions. The Sil8784 device supports PC resolutions up to 1600 x 1200 @ 60 Hz (UXGA).

## 3.2.1.6. SCART Fast Blanking

VDC is designed to support SCART interface: Composite, RGB, and Fast Blanking.

The 4 channel 10-bit ADCs in AFE are mapped to CVBS, RED, GRN, and BLU inputs of SCART interface. A color space converter converts the digitized RGB data from RGB to YUV (BT601). Then the YUV data are resampled from 108 MHz to the 8Fsc frequency used in the 2D comb filter, and meanwhile the YUV444 data are converted to YUV422. These YUV422 data matched the timing of the 2D comb filter output 8Fsc Y/C data, and the two data streams are blended together according to the FB signal information, which indicates the current display source is from original RGB or Composite inputs.

The SCART\_ASPECT information is from ASPECTO/1 comparator outputs of AFE, and their results are read-only status registers which can be handled by software.

## 3.2.2. Sync Processor

The Sync Processor block contains sophisticated digital circuitry that analyzes and extracts synchronization pulses from the incoming video stream. It generates filtered vertical and horizontal sync pulses. The Sync Processor includes Sync separation, format detection, and Sync stabilization.

Sync Separation

The Sync Separation separates the HSync and VSync from the composite sync sliced from video decoder or SOG slicer.

• Sync Stabilization

Sync Stabilization does de-glitch, removes serration, and equalizes pulses from the sync signal. It also detects Macrovision protection status.

Format Detection

The format detection detects vertical period and horizontal period and total line number per field.

## 3.2.3. VBI Decoder

The VBI Processing block slices and processes digitized VBI data from the video. Following are some of the features of the VBI block:

- 108 MHz operating with programmable down sampling

- Supports PAL standards

- Supports NTSC standards

- Enhanced Teletext parity and hamming 8/4 correction

Table 3.3 shows the supported VBI standards.

| VBI Standard            | Video<br>Standard | Data Rate                                   | Scan<br>Lines   | Data per<br>Line                                                       | Encoding                                                                       | Description                                                                    |

|-------------------------|-------------------|---------------------------------------------|-----------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| WSS 625                 | PAL SECAM         | 5 MHz                                       | 23<br>336       | 14 Bits                                                                | Phase Encoding.<br>Each bit is transmitted<br>using 6 bits of<br>encoded data. | Wide Screen Signaling.<br>Used for aspect ratio settings.                      |

| VPS                     | PAL SECAM         | AL SECAM 5 MHz 16 13 Bytes Each bit is effe |                 | Biphase Encoding.<br>Each bit is effectively<br>represented by 2 bits. | Video Programming System.<br>Used in Germany for<br>program/broadcast info.    |                                                                                |

| СС                      | NTSC              | 0.5030 MHz                                  | 21              | 2 Bytes                                                                | Parity.                                                                        | Closed Captioning for the hearing impaired.                                    |

| XDS<br>VChip            | NTSC              | 0.5035 MHz                                  | 284             | 2 Bytes                                                                | Parity.                                                                        | Extended Data Service.<br>Used for MISC. NTSC services.                        |

| WSS 525<br>ID-1<br>CGMS | NTSC              | 0.4474 MHz                                  | 20              | 14 Bits                                                                | CRC.                                                                           | Copy Guard Management System.<br>Used for copy protection and<br>aspect ratio. |

| Teletext                | PAL<br>SECAM      | 6.9375 MHz                                  | 6-22<br>318-334 | 42 Bytes                                                               | Encoded using parity,<br>hamming 8/4 and<br>hamming 24/18.                     | Teletext.<br>Used for data transmissions in<br>Europe.                         |

## Table 3.3. Supported Standards

# **3.3. Video Processing**

The video processing block performs some necessary processing functions to the decoded video streams before they are outputted. There are also some measurement blocks inside to implement automatic Phase/Position/Gain adjustment functions.

# 3.3.1. Time Base Corrector

The Time Base Corrector (TBC) is designed to provide stable clock and video data for HDMI/MHL output. It uses a line buffer based architecture in lieu of a frame buffer to save cost and power. To keep HDMI/MHL output TMDS clock jitter in a safe range, the TBC output field frequency is limited to 50 Hz  $\pm$ 0.5% or 59.94 Hz/60 Hz  $\pm$ 0.5% as default. If the field frequency of input video is beyond this range, the display will be scrolling.

Composite video formats are supported by the TBC. 480i/576i component formats can be supported by the TBC if needed.

# 3.3.2. VBI Post Processor

The VBI Post Processor is used to transmit VBI data to DTV over the HDMI/MHL connection.

In case the raw VBI data i.e. digitized luma portion of the incoming video signal, or Teletext need to be transmitted to DTV over HDMI/MHL, they are embedded into the video stream and transmitted. As the decoded VBI data, they can be transmitted over HDMI or MHL using Vendor Specific Info Frame (VSIF).

# 3.3.3. De-interlacer and Edge Smoother

De-interlacing is designed to convert an interlaced (480i/576i) video signal to a progressive (480p/576p) video signal. BOB de-interlacing method is adopted to reduce cost and power consumption. An edge smoother is included to reduce the saw tooth artifacts generated by de-interlacing and to improve the picture quality.

The de-interlacer and edge smoother must be used together with the TBC.

# 3.3.4. Color Processing

Color Processing (CP) enables brightness, contrast, saturation, and hue controls for end users. It supports YCbCr color space only.

# 3.3.5. Auto Phase Detection

The Auto Phase Detection (APD) is a module used to search for the phases that can generate the best display quality. The desired phases, in general, can generate sharp and stable images, if the input image meets certain criteria during phase detection period. APD is an automatic algorithm that can be enabled or disabled by software. It can be applied to both VGA and Component inputs.

# 3.3.6. Auto Position Calibration

The Auto Position Calibration (APC) detects the active picture area of input video signal and adjusts the output timing so that the final picture can fit to the display properly.

# 3.3.7. Auto Gain Calibration

Slight mismatch of analog input channels including offset and gain may impact the picture quality. The Sil8784 device has been designed to keep the mismatches in an acceptable range (<0.5 dB). It is still important to calibrate these mismatches in some cases to achieve the most accurate picture. To help manufacturers finish this process efficiently, an Auto Gain Calibration (AGCWIN) mechanism is designed in the Sil8784 device. This mechanism automatically measures the digitalized signal levels through the AGCWIN module, calculates the correct values, and stores them into the external SPI Flash memory. These values can be used by firmware in user mode to compensate the analog mismatches.

<sup>© 2012-2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

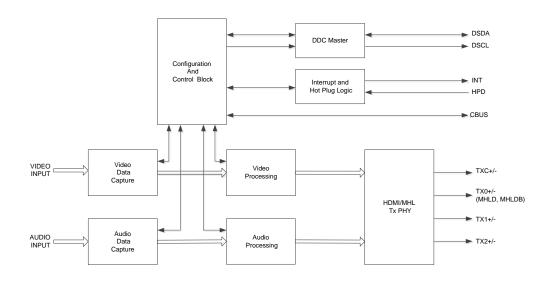

# 3.4. Dual-mode HDMI/MHL Transmitter

The Sil8784 device incorporates the latest HDMI 1.4 and MHL 2 dual-mode transmitter. It multiplexes video and audio data into the HDMI/MHL stream and performs TMDS encoding. It contains digital video data capture and its processing block, digital audio data capture and its processing block, HDMI/MHL transmitter, and PHY. Figure 3.6 shows the dual-mode HDMI/MHL transmitter diagram.

Figure 3.6. Dual-mode HDMI/MHL Transmitter Diagram

# 3.4.1. Video Data Capture Logic

The Video Data Capture Logic receives uncompressed digital video with a data width of 8 to 24 bits from the digital parallel video interface. The bus configurations support most standard video input formats as well as other widely used non-standard formats.

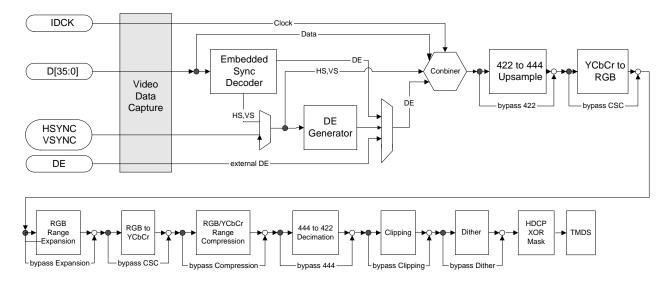

# 3.4.2. Video Processing Path

Figure 3.7 shows the video data processing stages. Each of the processing blocks can be bypassed by setting the appropriate register bits.

## Figure 3.7. Transmitter Video Data Processing Path Embedded Sync Decoder

The input processor can create DE, HSYNC, and VSYNC signals using the start of active video (SAV) and end of active video (EAV) codes within the ITU-R BT.656-format video stream.

#### 3.4.2.1. Data Enable Generator

The transmitter includes logic to construct a DE signal from the incoming HSYNC, VSYNC, and clock. Registers are programmed to enable the DE signal to define the size of the active display region.

#### 3.4.2.2. Combiner

The clock, data, and sync information is combined into a complete set of signals required for TMDS encoding. From here, the signals are manipulated by the register-selected video processing blocks.

#### 3.4.2.3. 422 to 444 Up-sampler

Chrominance up-sampling and down-sampling increase or decrease the number of chrominance samples in each line of video. Up-sampling doubles the number of chrominance samples in each line, converting 4:2:2 sampled video to 4:4:4 sampled video.

#### 3.4.2.4. 444 to 422 Decimation

Decimation reduces the number of chrominance samples in each line by half, converting 4:4:4 sampled video to 4:2:2 video.

#### 3.4.2.5. Color Space Converters (CSC)

Two color space converters (CSCs) (YCbCr to RGB and RGB to YCbCr) are available to interface to the many video formats supplied by A/V processors and to provide full DVI backward compatibility. The CSC can be adjusted to perform standard-definition conversions (ITU.601) or high-definition conversions (ITU.709) by setting the appropriate registers.

#### **RGB to YCbCr**

The RGB→YCbCr color space converter can convert from video data RGB to standard definition or to high definition YCbCr formats. The HDMI AVI packet defines the color space of the incoming video.

| Video Format | Conversion   | Formulas                                |

|--------------|--------------|-----------------------------------------|

| video Format | Conversion   | CE Mode 16-235 RGB                      |

| 640 x 480    | ITU-R BT.601 |                                         |

| 480i         | ITU-R BT.601 |                                         |

| 576i         | ITU-R BT.601 | Y = 0.299R' + 0.587G' + 0.114B'         |

| 480p         | ITU-R BT.601 | Cb = -0.172R' - 0.339G' + 0.511B' + 128 |

| 576p         | ITU-R BT.601 | Cr = 0.511R' - 0.428G' - 0.083B' + 128  |

| 240p         | ITU-R BT.601 |                                         |

| 288p         | ITU-R BT.601 |                                         |

| 720p         | ITU-R BT.709 | Y = 0.213R' + 0.715G' + 0.072B'         |

| 1080i        | ITU-R BT.709 | Cb = -0.117R' - 0.394G' + 0.511B' + 128 |

| 1080p        | ITU-R BT.709 | Cr = 0.511R' - 0.464G' - 0.047B' + 128  |

#### Table 3.4. Color Space Versus Video Format

#### YCbCr to RGB

The YCbCr→RGB color space converter allows MPEG decoders to interface with RGB-only inputs. The CSC can convert from YCbCr in standard-definition (ITU.601) or high-definition (ITU.709) to RGB. Refer to Table 3.5 for the detailed formulas. Note the difference between RGB range for CE modes and PC modes.

| Format Change                            | Conversion       | YCbCr Input Color Range 2, 3                                                                                                           |

|------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| YCbCr 16-235 Input <sup>2, 3</sup>       | 6011             | R' = Y + 1.371(Cr - 128)<br>G' = Y - 0.698(Cr - 128) - 0.336(Cb - 128)<br>B' = Y + 1.732(Cb - 128)                                     |

| to<br>RGB 16-235 Output <sup>2, 3</sup>  | 709 <sup>1</sup> | R' = Y + 1.540(Cr - 128)<br>G' = Y - 0.459(Cr - 128) - 0.183(Cb - 128)<br>B' = Y + 1.816(Cb - 128)                                     |

| YCbCr 16-235 Input <sup>2, 3</sup><br>to | 601              | R' = 1.164((Y-16) + 1.371(Cr - 128))<br>G' = 1.164((Y-16) - 0.698(Cr - 128) - 0.336(Cb - 128))<br>B' = 1.164((Y-16) + 1.732(Cb - 128)) |

| RGB 0-255 Output <sup>2, 3</sup>         | 709              | R' = 1.164((Y-16) + 1.540(Cr - 128))<br>G' = 1.164((Y-16) - 0.459(Cr - 128) - 0.183(Cb - 128))<br>B' = 1.164((Y-16) + 1.816(Cb - 128)) |

| Table 3.5. YCbCr-to-RGB Color Space Conversion |

|------------------------------------------------|

|------------------------------------------------|

Notes:

1. No clipping can be done.

2. For 10-bit deep color, all occurrences of the values 16, 128, 235, and 255 should be multiplied by 4.

3. For 12-bit deep color, all occurrences of the values 16, 128, 235, and 255 should be multiplied by 16.

#### 3.4.2.6. RGB Range Expansion

The Sil8784 input processor can scale the input color from limited-range into full-range using the range expansion block. When enabled by itself, the range expansion block expands 16 - 235 limited-range data into 0 - 255 for each video channel. When the range expansion and the YCbCr to RGB color space converter are both enabled, the input conversion range for the Cb and Cr channels is 16 - 240.

#### 3.4.2.7. RGB/YCbCr Range Compression

When enabled by itself, the Range Compression Block compresses 0 - 255 full-range data into 16 - 235 limited-range data for each video channel. When enabled with the RGB to YCbCr converter, this block compresses to 16 - 240 for the Cb and Cr channels. The color range scaling is linear.

#### 3.4.2.8. Clipping

The clipping block, when enabled, clips the values of the output video to 16 - 235 for RGB video or the Y channel, and to 16 - 240 for the Cb and Cr channels.

### 3.4.2.9. Dither

The dither block dithers internally processed data to 8, 10, or 12 bits for output on the HDMI link.

### 3.4.2.10. HDCP Encryption Engine/XOR Mask

The HDCP encryption engine contains the logic necessary to encrypt the incoming audio and video data and includes support for HDCP authentication and repeater checks. The system microcontroller or microprocessor controls the encryption process by using a set sequence of register reads and writes. An algorithm uses HDCP keys and a Key Selector Value (KSV) stored in the on-board ROM to calculate a number that is then applied to an XOR mask. This process encrypts the audio and video data on a pixel-by-pixel basis during each clock cycle.

## 3.4.2.11. TMDS Digital Core

The TMDS digital core performs 8-to-10-bit TMDS encoding on the data received from the HDCP XOR mask. This data is sent to three TMDS differential data lines, along with a TMDS differential clock line. A resistor tied to the EXT\_SWING pin controls the TMDS swing amplitude.

## 3.4.3. Audio Data Capture and Processing Logic

The Sil8784 device accepts digital audio over an S/PDIF interface, four I<sup>2</sup>S inputs, or eight one-bit audio inputs.

## 3.4.3.1. S/PDIF

The S/PDIF stream can carry 2-channel uncompressed PCM data (IEC 60958) or a compressed bit stream for multi-channel (IEC 61937) formats. The audio data capture logic forms the audio data into packets described in the HDMI Specification. The S/PDIF input supports audio sampling (Fs) rates from 32 to 192 kHz. A separate master clock input (MCLK), coherent with the S/PDIF input, is required for time-stamping purposes. *Coherent* means that the MCLK and S/PDIF have been created from the same clock source. This step usually uses the original MCLK to strobe out the S/PDIF from the sourcing chip. There is no setup or hold timing requirement on an input with respect to MCLK.

## 3.4.3.2. I<sup>2</sup>S

Four I<sup>2</sup>S inputs allow transmission of DVD-Audio or decoded Dolby Digital to A/V receivers and high-end displays. The interface works in slave mode, supports sample rate up to 192 kHz.

Register control allows the audio data to be down-sampled by one-half or one-fourth, so that the transmitter can be compatible with the attached display that supports lower sample rate audio only. Conversions from 192 to 48 kHz, from 176.4 to 44.1 kHz, from 96 to 48 kHz, and from 88.2 to 44.1 kHz are supported. Audio data can only be down-sampled on 2-channel audio.

The appropriate registers must be configured to describe the audio format provided to the Sil8784 input processor. This information is passed over the HDMI link in the CEA-861D Audio Info (AI) packets.

Table 3.6 shows the MCLK frequencies that support seven audio sample rates.

|                | I <sup>2</sup> S and S/PDIF Supported MCLK Rates |            |            |            |            |            |            |  |  |  |  |

|----------------|--------------------------------------------------|------------|------------|------------|------------|------------|------------|--|--|--|--|

| Multiple of Fs | Audio Sample Rate, Fs                            |            |            |            |            |            |            |  |  |  |  |

|                | 32 kHz                                           | 44.1 kHz   | 48 kHz     | 88.2 kHz   | 96 kHz     | 176.4 kHz  | 192 kHz    |  |  |  |  |

| 128            | 4.096 MHz                                        | 5.645 MHz  | 6.144 MHz  | 11.290 MHz | 12.288 MHz | 22.579 MHz | 24.576 MHz |  |  |  |  |

| 192            | 6.144 MHz                                        | 8.467 MHz  | 9.216 MHz  | 16.934 MHz | 18.432 MHz | 33.868 MHz | 36.864 MHz |  |  |  |  |

| 256            | 8.192 MHz                                        | 11.290 MHz | 12.288 MHz | 22.579 MHz | 24.576 MHz | 45.158 MHz | 49.152 MHz |  |  |  |  |

| 384            | 12.288 MHz                                       | 16.934 MHz | 18.432 MHz | 33.864 MHz | 36.864 MHz | 67.737 MHz | 73.728 MHz |  |  |  |  |

| 512            | 16.384 MHz                                       | 22.579 MHz | 24.576 MHz | 45.158 MHz | 49.152 MHz | _          | —          |  |  |  |  |

| 768            | 24.576 MHz                                       | 33.869 MHz | 36.864 MHz | 67.738 MHz | 73.728 MHz | _          | —          |  |  |  |  |

| 1024           | 32.768 MHz                                       | 45.158 MHz | 49.152 MHz | —          | _          | —          | —          |  |  |  |  |

| 1152           | 36.864 MHz                                       | 50.803 MHz | 55.296 MHz | _          | _          | _          | —          |  |  |  |  |

#### Table 3.6. Supported MCLK Frequencies

# 3.5. Control Logic

## 3.5.1. Internal Microcontroller

As shown in Figure 3.1 on page 7, an 8-bit 8051 compatible microcontroller is integrated in the Sil8784 device. It contains 3 KB data RAM and 96 KB code RAM. The code can be loaded into code RAM from external SPI Flash or EEPROM memory automatically after power on. If the check sum of the code data is correct, the code will be executed. Otherwise the internal microcontroller is disabled and the chip can be controlled by external controller through I<sup>2</sup>C bus. The internal controller can access all the internal registers directly over the internal bus. The 8051 microcontroller runs at the crystal clock of 24 MHz.

When the booting procedure is finished, the SPI interface will be handed over to the 8051 SPI module so that firmware can read/write the external memory if needed.

The internal controller can also operate other peripherals through the I<sup>2</sup>C bus of the SiI8784 device by setting it to the master mode.

#### 3.5.1.1. Data Structure of External SPI Memory

Figure 3.8 shows the memory structure which is required for the internal microcontroller to load the code correctly.

Figure 3.8. External Memory Structure

| Table | 3.7  | Head  | Flags |

|-------|------|-------|-------|

| Iable | 3.7. | iieau | riago |

| EEPROM/Flash Address | EEPROM/Flash Content |

|----------------------|----------------------|

| 00000Н               | Head0 'S'            |

| 00001H               | Head1 'I'            |

| 00002H               | Head2 'M'            |

| 00003H               | Head3 'G'            |

Note: The head flag will be four bytes ASCII code of 'S', 'I', 'M', 'G'.

#### Table 3.8. Info Bytes

| EEPROM/Flash Address | EEPROM/Flash Content             |

|----------------------|----------------------------------|

| 00004H               | SPI PARAMETER.                   |

| 00005H               | Calibration Version (low byte)   |

| 00006H               | Calibration Version.             |

| 00007H               | Calibration Version (high byte). |

| 00008H               | Code Version (low byte).         |

| 00009Н               | Code Version.                    |

| 0000AH               | Code Version (high byte).        |

| 0000ВН               | Reserved.                        |

| 0000CH               | Reserved.                        |

| 0000DH               | Reserved.                        |

| 0000EH               | Reserved.                        |

| 0000FH               | Reserved.                        |

**Note**: The info bytes contain the information about the feature of Max read frequency of external EEPROM/Flash, the calibration version, and the code version. It occupies 12 bytes.

#### Table 3.9. SPI Parameter

| SPI Parameter | Description                                  |

|---------------|----------------------------------------------|

| 0x00          | 2 MHz baud rate to access SPI Flash/EEPROM.  |

| 0x01          | 24 MHz baud rate to access SPI Flash/EEPROM. |

## Table 3.10. Calibration Checksum

| EEPROM/Flash Address EEPROM/Flash Content |                                   |

|-------------------------------------------|-----------------------------------|

| 0010EH                                    | Calibration Checksum (low byte).  |

| 0010FH                                    | Calibration Checksum (high byte). |

Note: The calibration checksum is two bytes which locates at the last site of 256 size calibration data.

#### Table 3.11. HW Configuration Data

| EEPROM/Flash Address | EEPROM/Flash Content      |

|----------------------|---------------------------|

| 00110H               | BT_SPI_PINMUX_SEL.        |

|                      | 00H – SPI function        |

|                      | 01H – Reserved. Don't use |

|                      | 02H – Reserved. Don't use |

| 00111H0012FH         | Reserved.                 |

## Table 3.12. 8051 Code Size

| EEPROM/Flash Address | EEPROM/Flash Content   |

|----------------------|------------------------|

| 00130H               | Code Size (low byte).  |

| 00131H               | Code Size.             |

| 00132H               | Code Size (high byte). |

### Table 3.13. HW Configuration Data and Code Checksum

| EEPROM/Flash Address | EEPROM/Flash Content           |

|----------------------|--------------------------------|

| 00133H + code size   | Code Checksum0 (lowest byte).  |

| 00134H + code size   | Code Checksum1.                |

| 00135H + code size   | Code Checksum2.                |

| 00136H + code size   | Code Checksum3 (highest byte). |

The boot module tries to load data from external device and write into chip SRAM. The 8051 code content is written into the 96K bytes SRAM of 8051. The 256 system calibration is written into the high 3 K bytes SRAM in data memory.

For details on the selection of the SPI Flash memory, refer to the relevant Application Note (SiI-AN-1108).

# 3.5.2. Registers

The register block incorporates all the registers required for configuring and managing the Sil8784 device. These registers are used to perform AFE processing, VDC processing, MHL/HDMI processing, and all other control functions.

# 3.5.3. I<sup>2</sup>C Bus

The local I<sup>2</sup>C slave bus provides the host with communication to the entire system. The controller I<sup>2</sup>C interface on the Sil8784 device (signals CSCL and CSDA) is a slave interface, which is capable of running up to 400 kHz.

All functions of the Sil8784 device are controlled and observed with I<sup>2</sup>C registers. Device addresses can be altered with the level of the Cl2CA signal. Table 3.14 shows the device addresses as altered by the level of the Cl2CA signal.

| CI2CA = 0 | CI2CA = 1 | Purpose                                      |

|-----------|-----------|----------------------------------------------|

| 0x8C      | 0x8E      | System Control and Status                    |

| 0x84      | 0x84      | VD_DPGA<br>VD_SIGNALROUTING                  |

| 0x86      | 0x86      | VD_VBI                                       |

| 0x8A      | 0x8A      | VD_VDREG<br>VD_ADCIF                         |

| 0x92      | 0x92      | VD_SYNCPROC                                  |

| 0x96      | 0x96      | VD_ADCSTATUS<br>VD_VPP<br>Edge Smooth<br>INT |

| 0xDA      | 0xDA      | FPGA<br>APD<br>ADC_WIN                       |

| 0x9C      | 0x9C      | VidPath<br>Calibration                       |

| 0xD8      | 0xD8      | AFE                                          |

| 0x72      | 0x76      | HW_TPI<br>TX Page 0/2                        |

| 0x7A      | 0x7E      | TX Page 1                                    |

| 0x90      | 0x94      | Reserved                                     |

| 0xC0      | 0xC4      | CEC 1.6                                      |

| 0x60      | 0x60      | ТХ РНҮ                                       |

| 0xC8      | 0xCC      | CBUS                                         |

Table 3.14. Control of Transmitter I<sup>2</sup>C Address with CI2CA Signal

**Note**: When the internal microcontroller is enabled, the I<sup>2</sup>C bus is taken over by the firmware. It can work as both master and slave mode, and the addresses are alterable.

# 3.5.4. Interrupt

The Sil8784 device contains a configurable interrupt generator with an open-drain type output pin. It can be used to notify application processor (if there is application processor) to handle some events.

# 3.5.5. GPIOs

There are five general purpose IO pins on the SiI8784 device. Generally they can be used to detect the cable plug-in status, but they can be used for other purposes as well.

#### Table 3.15. List of GPIOs

| Name               | Туре | Pull up/down <sup>2</sup> Reset Status |   |

|--------------------|------|----------------------------------------|---|

| GPIO0 <sup>1</sup> | 10   | Pull down                              | I |

| GPIO1              | 10   | Pull up                                | I |

| GPIO2              | 10   | Pull up                                | I |

| GPIO3              | 10   | Pull up                                | I |

| GPIO4              | 10   | Pull up                                | I |

Notes:

1. GPIO0 is also used as CI2CA pin to decide the  $I^2C$  slave address during reset.

2. The internal Pull up/down resistors are fixed and weak just to avoid floating input level when they are left unconnected. Peripheral circuits should not rely on them. 10 K or smaller resistors are recommended for external pull up/down circuit to override them if needed.

# 4. Electrical Specifications

# 4.1. Absolute Maximum Conditions

## Table 4.1. Absolute Maximum Ratings

| Symbol                   | Parameter                          | Min  | Тур | Max          | Units | Notes |

|--------------------------|------------------------------------|------|-----|--------------|-------|-------|

| VP2V5A                   | Analog Power for ADC               | -0.3 | —   | 3.0          | V     | 1, 2  |

| VP2V5D                   | Digital Power for ADC              | -0.3 | —   | 3.0          | V     | 1, 2  |

| VP2V5_SLICER             | Analog Power for SOG Slicer        | -0.3 | —   | 3.0          | V     | 1, 2  |

| VP1V0_PLL                | Power for APLL and LLPLL           | -0.3 | _   | 1.2          | V     | 1, 2  |

| VCC10_TPLL               | TCI PLL Power                      | -0.3 | —   | 1.2          | V     | 1, 2  |

| AVCC_PLL                 | Analog PLL Power of HDMI/MHLTX     | -0.3 | _   | 1.2          | V     | 1, 2  |

| AVCC                     | Power for HDMI/MHL TX              | -0.3 | —   | 1.2          | V     | 1, 2  |

| AVCC3V3_CBUS             | Power for CBUS I/O                 | -0.3 | _   | 4.0          | V     | 1, 2  |

| CVCC10                   | Power for Digital Core             | -0.3 | _   | 1.2          | V     | 1, 2  |

| VDDIO3V3                 | Power for Digital I/O              | -0.3 | _   | 4.0          | V     | 1, 2  |

| XTALVCC33                | Power for XTAL                     | -0.3 | —   | 4.0          | V     | 1, 2  |

| VI                       | Digital Input Voltage              | -0.3 | _   | VDDIO + 0.3  | V     | 1, 2  |

| Vo                       | Digital Output Voltage             | -0.3 | —   | VDDIO + 0.3  | V     | 1, 2  |

| AVI                      | Analog Input Voltage               | -0.3 | —   | VP2V5A + 0.3 | V     | 1, 2  |

| V <sub>5V-Tolerant</sub> | Input Voltage on 5 V Tolerant Pins | -0.3 | _   | 5.5          | V     | _     |

| Tj                       | Junction Temperature               | -    | —   | 125          | °C    | —     |

| T <sub>STG</sub>         | Storage Temperature                | -65  | —   | 150          | °C    | —     |

#### Notes:

1. Permanent device damage can occur if absolute maximum conditions are exceeded.

2. Functional operation should be restricted to the conditions described under normal operating conditions.

# 4.2. Normal Operating Conditions

#### Table 4.2. Normal Operating Conditions

| Symbol                    | Parameter                                | Min   | Тур  | Max   | Units | Notes |

|---------------------------|------------------------------------------|-------|------|-------|-------|-------|

| VP2V5A                    | Analog Power for ADC                     | 2.375 | 2.50 | 2.625 | V     | 2     |

|                           |                                          | —     | 350  | _     | mA    | 4, 8  |

|                           | Total Current Consumption of VP2V5A      | _     | 90   | _     | mA    | 5, 8  |

| I <sub>VP2V5A</sub>       | Total current consumption of VP2VSA      | _     | 260  | —     | mA    | 6, 8  |

|                           |                                          | _     | 260  | _     | mA    | 7, 8  |

| VP2V5D                    | Digital Power for ADC                    | 2.375 | 2.50 | 2.625 | V     | _     |

|                           |                                          | _     | 9    | —     | mA    | 4, 8  |

| I <sub>VP2V5D</sub>       | Total Current Consumption of VP2V5D      | _     | 2.5  | -     | mA    | 5, 8  |

| 1002050                   |                                          | —     | 9    | —     | mA    | 6, 8  |

|                           |                                          | —     | 10   | —     | mA    | 7, 8  |

| VP2V5_SLICER              | Analog Power for SOG Slicer              | 2.375 | 2.50 | 2.625 | V     | 2     |

| IVP2V5_SLICER             | Current Consumption of VP2V5_SLICER      | —     | 3    | —     | mA    | 6, 8  |

| VP1V0_PLL                 | Power for APLL and LLPLL                 | 0.95  | 1.00 | 1.05  | V     | 3     |

| IVP1V0_PLL                | Current Consumption of VP1V0_PLL         | _     | 20   | —     | mA    | 7, 8  |

| VCC10_TPLL                | TCI PLL Power                            | 0.95  | 1.00 | 1.05  | V     | 3     |

| IVCC10_TPLL               | Current Consumption of VCC10_TPLL        | —     | 3.5  | _     | mA    | 5, 8  |

| AVCC_PLL                  | Analog PLL Power of HDMI/MHLTX           | 0.95  | 1.00 | 1.05  | V     | 3     |

|                           | Current Consumption of AV/CC, DU         | _     | 4.5  | _     | mA    | 7, 8  |

| AVCC_PLL                  | Current Consumption of AVCC_PLL          | —     | 8.5  | —     | mA    | 6, 9  |

| AVCC                      | Power for HDMI/MHL TX                    | 0.95  | 1.00 | 1.05  | V     | _     |

|                           | Current Consumption of AVCC              | —     | 4.5  | _     | mA    | 7, 8  |

| I <sub>AVCC</sub>         |                                          | _     | 10   | _     | mA    | 6, 9  |

| CVCC10                    | Power for Digital Core                   | 0.95  | 1.00 | 1.05  | V     | _     |

|                           |                                          | —     | 70   | _     | mA    | 4, 8  |

|                           |                                          | —     | 65   | —     | mA    | 5, 8  |

|                           |                                          | —     | 80   | —     | mA    | 6, 8  |

| I <sub>CVCC10</sub>       | Total Current Consumption of CVCC10      | _     | 85   | _     | mA    | 7, 8  |

|                           |                                          | _     | 85   | _     | mA    | 4, 9  |

|                           |                                          | _     | 70   | —     | mA    | 5, 9  |

|                           |                                          | —     | 100  | —     | mA    | 6, 9  |

| VDDIO3V3                  | Power for Digital I/O                    | 3.135 | 3.30 | 3.465 | V     | —     |

|                           |                                          | —     | 2    | -     | mA    | 4, 8  |

|                           |                                          | —     | 2    | -     | mA    | 5,8   |

|                           |                                          | —     | 7    | —     | mA    | 6, 8  |

| I <sub>VDDIO3V3</sub>     | Current Consumption of VDDIO3V3          | —     | 8    | —     | mA    | 7,8   |

|                           |                                          | —     | 40   | —     | mA    | 4, 9  |

|                           |                                          | -     | 55   | —     | mA    | 5, 9  |

|                           |                                          | -     | 60   | —     | mA    | 6, 9  |

| AVCC3V3_CBUS              | Power for CBUS I/O                       | 3.135 | 3.30 | 3.465 | V     | _     |

| I <sub>AVCC3V3_CBUS</sub> | Current Consumption of AVCC3V3_CBUS      | -     | 8    | -     | mA    | 6, 9  |

| XTALVCC33                 | Power for XTAL                           | 3.135 | 3.30 | 3.465 | V     | _     |

| I <sub>XTALVCC33</sub>    | Current Consumption of XTALVCC33         | -     | 3.5  | —     | mA    | 6, 8  |

| ТА                        | Ambient Temperature (with power applied) | 0     | 25   | 70    | °C    | _     |

| $\Theta_{ja}$             | Ambient Thermal Resistance (Theta JA)    | -     | -    | 25.6  | °C/W  | 1     |

#### **Table 4.2. Normal Operating Conditions (Continued)**

| Symbol            | Parameter                          | Min | Тур | Max  | Units | Notes |

|-------------------|------------------------------------|-----|-----|------|-------|-------|

| $\Theta_{\sf jc}$ | Case Thermal Resistance (Theta JC) |     |     | 11.9 | _     | —     |

Notes:

- 1. Airflow at 0 m/s. Package ePad soldered to PCB.

- 2. The power ripple must be below 60 mVpp to avoid video quality detrition.

- 3. Avoid any noise coupling to PLL power rails.

- 4. Measured with SCART input.

- 5. Measured with CVBS input.

- 6. Measured with YPbPr 1080p60 input.

- 7. Measured with UXGA60 input.

- 8. HDMI output mode.

- 9. MHL output mode.

# 4.3. ESD Specifications

## Table 4.3. ESD Specifications

| Symbol   | Parameter            | Min   | Тур | Max | Units | Notes |

|----------|----------------------|-------|-----|-----|-------|-------|

| Latch up | ESD Latch up         | ± 200 |     |     | mA    | 1, 2  |

| НВМ      | Human Body Model     | 2000  | -   | -   | V     | 3     |

| MM       | Machine Model        | 200   | _   | -   | V     | 4     |

| CDM      | Charged Device Model | 500   | -   |     | V     | 5     |

Notes:

- 1. At 70 °C.

- 2. Measured as per JESD78B standard.

3. Measured as per JESD22-A114 standard.

4. Measured as per JESD22-A115 standard.

5. Measured as per JESD22-C101 standard.

# 4.4. DC Specifications

#### Table 4.4. Digital I/O Specifications

| Symbol              | Parameter                                                      | Conditions                        | Min  | Тур  | Max  | Units                                                                                                                                                                           | Notes |  |

|---------------------|----------------------------------------------------------------|-----------------------------------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Digital Input       | ts                                                             |                                   |      |      |      | -     V       77     V       35     V       10     μA       59     KΩ       30     KΩ       -     V       .5     V       -     V       9.8     V       9.7     KΩ       -     V |       |  |

| VIL                 | Input Low Voltage                                              | _                                 | _    | _    | 0.8  | V                                                                                                                                                                               | 1     |  |

| V <sub>IH</sub>     | Input High Voltage                                             | _                                 | 2.0  | _    | _    | V                                                                                                                                                                               | 1     |  |

| $V_{\text{TH+}}$    | Schmitt Trigger LOW to HIGH Threshold                          | _                                 | 1.61 | 1.69 | 1.77 | V                                                                                                                                                                               | 1     |  |

| V <sub>TH-</sub>    | Schmitt Trigger HIGH to LOW threshold                          | _                                 | 1.18 | 1.27 | 1.35 | V                                                                                                                                                                               | 1     |  |

| IIL                 | Input Leakage Current                                          | _                                 | -10  | _    | 10   | μΑ                                                                                                                                                                              | 1     |  |

| RPU                 | Pull-up Resistor                                               | _                                 | 27   | 38   | 59   | ΚΩ                                                                                                                                                                              | 1     |  |

| RPD                 | Pull-down Resistor                                             | _                                 | 31   | 46   | 80   | ΚΩ                                                                                                                                                                              | 1     |  |

| V <sub>TH+DDC</sub> | Schmitt Trigger LOW to HIGH Threshold of<br>DSCL and DSDA Pins | _                                 | 3    | -    | _    | V                                                                                                                                                                               | -     |  |

| V <sub>TH-DDC</sub> | Schmitt Trigger HIGH to LOW Threshold of<br>DSCL and DSDA Pins | _                                 | _    | -    | 1.5  | V                                                                                                                                                                               | -     |  |

| V <sub>TH+CEC</sub> | Schmitt Trigger LOW to HIGH Threshold of CEC Pin               | _                                 | 2    | -    | _    | V                                                                                                                                                                               | -     |  |

| V <sub>TH-CEC</sub> | Schmitt Trigger HIGH to LOW Threshold of CEC Pin               | -                                 | _    | _    | 0.8  | V                                                                                                                                                                               | -     |  |

| RPUCEC              | Pull-up Resistor on CEC Pin                                    | _                                 | 24.3 | 27   | 29.7 | ΚΩ                                                                                                                                                                              | _     |  |

| V <sub>TH+I2C</sub> | Schmitt Trigger LOW to HIGH Threshold of                       | _                                 | 2.0  | _    | —    | V                                                                                                                                                                               | 2     |  |

|                     | LSCL and LSDA Pins                                             | _                                 | 3.0  | _    | —    | V                                                                                                                                                                               | 3     |  |

| V <sub>TH-I2C</sub> | Schmitt Trigger HIGH to LOW Threshold of                       | _                                 | _    | _    | 0.8  | V                                                                                                                                                                               | 2     |  |

|                     | LSCL and LSDA Pins                                             | _                                 | -    | _    | 1.5  | V                                                                                                                                                                               | 3     |  |

| Digital Outp        | outs                                                           |                                   |      |      |      |                                                                                                                                                                                 | •     |  |

| V <sub>OH</sub>     | HIGH-level Output Voltage                                      | I <sub>ОН</sub> = 8mA             | 2.4  | _    | _    | V                                                                                                                                                                               | 1     |  |

| V <sub>OL</sub>     | LOW-level Output Voltage                                       | I <sub>OL</sub> = -8mA            | _    | _    | 0.4  | V                                                                                                                                                                               | 1     |  |

| I <sub>OZ</sub>     | Tri-state Output Leakage Current                               | _                                 | -10  | _    | 10   | μΑ                                                                                                                                                                              | 1     |  |

| $V_{OH\_CEC}$       | HIGH-level Output Voltage of CEC Pin                           | $I_{\text{OH}} = 100 \mu\text{A}$ | 2.5  | —    | —    | V                                                                                                                                                                               | —     |  |

| $V_{OL\_CEC}$       | LOW-level Output Voltage of CEC Pin                            | I <sub>OL</sub> = −100μA          | _    | _    | 0.4  | V                                                                                                                                                                               | _     |  |

Notes:

1. Applies to general digital IOs.

2. Compatible to 3.3 V I<sup>2</sup>C level in default.

3. Compatible to 5 V DDC level (need to be configured by register).

#### Table 4.5. HDMI TMDS Output DC Specifications

| Symbol             | Parameter                                 | Conditions               | Min                    | Тур | Мах                    | Units |

|--------------------|-------------------------------------------|--------------------------|------------------------|-----|------------------------|-------|

| V <sub>SWING</sub> | Single-ended Output Swing Voltage         | $R_{LOAD}$ = 50 $\Omega$ | 400                    | _   | 600                    | mV    |

| V <sub>H</sub>     | Single-ended High-level Output Voltage    | —                        | AV <sub>CC</sub> – 200 | —   | AV <sub>CC</sub> + 10  | mV    |

| VL                 | Single-ended Low-level Output Voltage     | _                        | AV <sub>CC</sub> – 700 | _   | AV <sub>CC</sub> – 400 | mV    |

| I <sub>DOS</sub>   | Differential output short-circuit current | VOUT = 0 V               | -                      | _   | 5                      | μΑ    |

| Symbol               | Parameter                                 | Conditions          | Min                      | Тур | Max                     | Units |

|----------------------|-------------------------------------------|---------------------|--------------------------|-----|-------------------------|-------|

| V <sub>SE_HIGH</sub> | Single-ended HIGH-level Output voltage    | —                   | V <sub>TERM</sub> - 540  |     | V <sub>TERM</sub> + 10  | mV    |

| V <sub>SE_LOW</sub>  | Single-ended LOW-level Output voltage     | —                   | V <sub>TERM</sub> - 1760 | -   | V <sub>TERM</sub> - 700 | mV    |

| V <sub>OFF</sub> *   | Single-ended Standby (off) Output Voltage | —                   | V <sub>TERM</sub> -10    | -   | V <sub>TERM</sub> + 10  | mV    |

| VDFSWING             | Differential Output Swing Amplitude       | RLOAD = 50 $\Omega$ | 600                      | -   | 1000                    | mV    |

| V                    | Common Mode Output Swing                  | RLOAD = 50 Ω        | 360                      |     | Min (720,               | mV    |

| V <sub>CMSWING</sub> | Common Mode Output Swing                  | single-ended        | 500                      |     | 0.85×VDFSWING)          | IIIV  |

## Table 4.6. MHL TMDS Output DC Specifications

#### \* Note:

$V_{OFF}$  is the source output voltage when terminated to  $V_{TERM}$  through  $R_{T1}$ , and the source device is in standby mode or power off mode.

| Symbol                   | Parameter                      | Conditions                                                                                                                                                                                                                                                | Min                                                   | Тур  | Max   | Units |

|--------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|-------|-------|

| V <sub>TERM_CBUS</sub>   | CBUS Termination Voltage       | _                                                                                                                                                                                                                                                         | 1.7                                                   | _    | 1.9   | V     |

| V <sub>IH_CBUS</sub>     | HIGH-level Input Voltage       | _                                                                                                                                                                                                                                                         | 1.0                                                   | _    | _     | V     |

| VIL_CBUS                 | LOW-level Input Voltage        | <u> </u>                                                                                                                                                                                                                                                  |                                                       |      | 0.6   | V     |

| V <sub>OH_CBUS</sub>     | HIGH-level Output Voltage      | IOVCC18 = 1.8 V, 85 °C                                                                                                                                                                                                                                    | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |      |       | V     |